## Modicon TSX Quantum 140 EHC 105 00 User Manual

# 140 EHC 105 00 High Speed Counter Module for Modicon TSX Quantum

**User Manual**

Version 1.01

840 USE 443 00

06/1997

#### Data, Illustrations, Alterations

Data and illustrations are not binding. We reserve the right to alter products in line with our policy of continuous product development. If you have any suggestions for improvements or amendments or have found errors in this publication, please notify us using the form on one of the last pages of this publication.

#### Training

Schneider Automation GmbH offers suitable further training on the system.

#### Hotline

See addresses for the Technical Support Centers at the end of this publication.

#### Trademarks

All terms used in this publication to denote Schneider Automation GmbH products are trademarks of Schneider Automation GmbH.

All other terms used in this publication to denote products may be registered trademarks and/or trademarks of the corresponding Corporations.

Microsoft and MS-DOS are registered trademarks of Microsoft Corporation, Windows is a brandname of Microsoft Corporation in the USA and other countries.

IBM is a registered trademark of International Business Machines Corporation.

Intel is a registered trademark of the Intel Corporation.

#### Copyright

All rights are reserved. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including copying, processing or by online file transfer, without permission in writing by Schneider Automation GmbH. You are not authorized to translate this document into any other language.

© 1997 Schneider Automation GmbH. All rights reserved

### **Contents**

| Chapter 1 | Introduction to the EHC 105                                                                                 | . 1 |

|-----------|-------------------------------------------------------------------------------------------------------------|-----|

| 1.1       | Introduction                                                                                                | 2   |

| 1.1.1     | General                                                                                                     |     |

| 1.1.2     | Using Concept and Modsoft                                                                                   |     |

| 1.2       | Operational Characteristics                                                                                 |     |

| 1.2.1     | EHC 105 Counter Channel Principles                                                                          |     |

| 1.2.2     | Description of the Individual Signals                                                                       |     |

| 1.2.3     | Output Set Point Mode (Absolute, Relative)                                                                  |     |

| 1.2.3.1   | Absolute Output Set Point Mode                                                                              | 11  |

| 1.2.3.2   | Relative Output Set Point Mode                                                                              | 11  |

| 1.2.4     | Start and Stop Function Priority Rankings                                                                   | 11  |

| 1.2.5     | Counting Direction Determination                                                                            |     |

| 1.2.6     | Overview and Relationships of Counter Functionality Features                                                |     |

| 1.3       | EHC 105 Counter Types                                                                                       |     |

| 1.3.1     | The Event Counter                                                                                           | 17  |

| 1.3.1.1   | Operating modes 1 and 8 (Event counter with                                                                 |     |

|           | relative Output Set Point Value and parallel Set Point activation)                                          | 18  |

| 1.3.1.2   | Operating modes 2 and 9 (Event counter with                                                                 |     |

|           | relative Output Set Point Value and serial Set Point activation)                                            | 19  |

| 1.3.1.3   | Operation mode A (Event counter with                                                                        | ~   |

| 4044      | absolute Output Set Point Value and timed output activation)                                                | 20  |

| 1.3.1.4   | Operation–mode B (Event counter with                                                                        | - 4 |

| 4.0.0     | absolute Output Set Point Value and latched output activation)                                              |     |

| 1.3.2     | The Differential Counter                                                                                    | 22  |

| 1.3.2.1   | Operating mode 3 (Differential counter with relative Output Set Point Value and parallel output activation) | 25  |

| 1.3.2.2   | Operating mode 4 (Differential counter with                                                                 | 23  |

| 1.3.2.2   | relative Output Set Point Value and serial output activation)                                               | 25  |

| 1.3.3     | The Repetitive Counter (Operating mode 5)                                                                   |     |

| 1.3.4     | The Rate Counter (Operating mode 6 or 7)                                                                    |     |

| 1.4       | State RAM Structure                                                                                         |     |

| 1.4.1     | Input Structure                                                                                             |     |

| 1.4.2     | Output Structure                                                                                            |     |

| 1.5       | Monitoring Capabilities                                                                                     |     |

| 1.5.1     | Input Signal Monitoring                                                                                     |     |

| 1.5.2     | Quantum System Bus Monitoring                                                                               |     |

| 1.5.3     | US24 Power Monitoring                                                                                       |     |

| 1.6       | EHC 105 Start-Up Characteristics                                                                            |     |

|           |                                                                                                             |     |

000000.20 Contents III

| Chapter 2 | Configuration                                                                  | 37  |

|-----------|--------------------------------------------------------------------------------|-----|

| 2.1       | Hardware and Software Prerequisites                                            | 38  |

| 2.2       | Configuration Steps                                                            |     |

| 2.2.1     | Configuration Steps for Installation                                           |     |

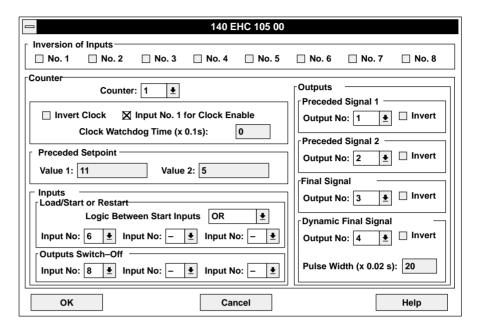

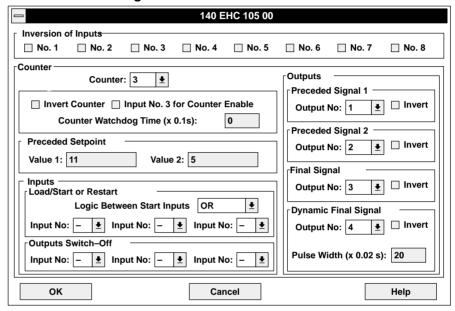

| 2.2.2     | Configuration using Concept (>= 2.0)                                           |     |

| 2.2.2.1   | Drop configuration (slot and I/O map)                                          |     |

| 2.2.2.2   | Configuration of counter characteristics under Concept                         |     |

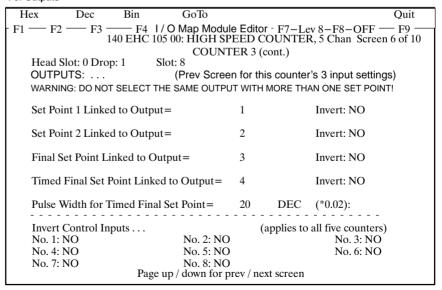

| 2.2.3     | Configuration under Modsoft (>= 2.4)                                           |     |

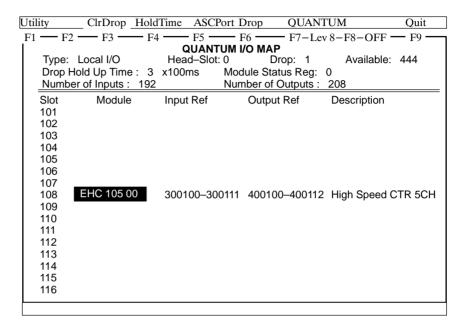

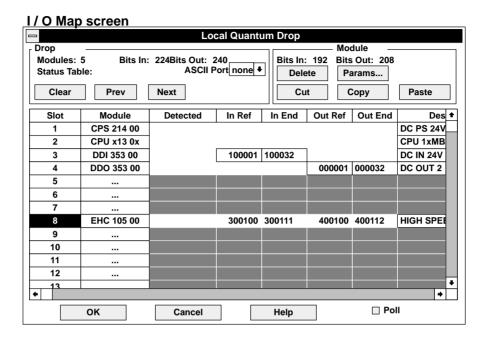

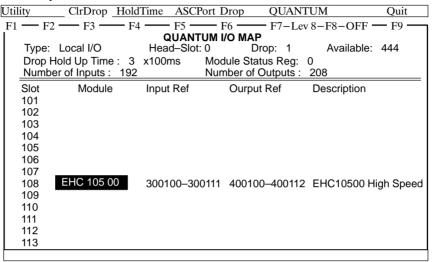

| 2.2.3.1   | I / O Map screen                                                               |     |

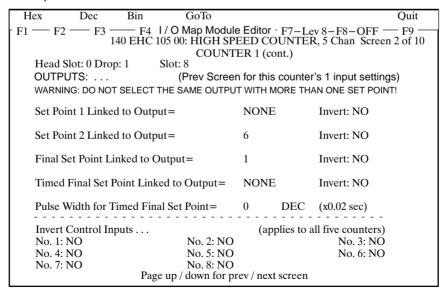

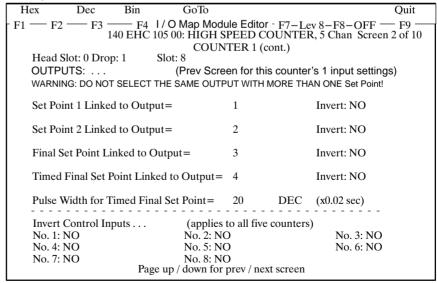

| 2.2.3.2   | Configuration of counter characteristics under Modsoft                         | 43  |

| Chapter 3 | Configuration Examples                                                         | 45  |

| 3.1       | Example 1: Event Counter (Up)                                                  |     |

| 3.1       | with parallel Set Point output activation, counter 1, mode 1                   | 46  |

| 3.1.1     | Specifications                                                                 |     |

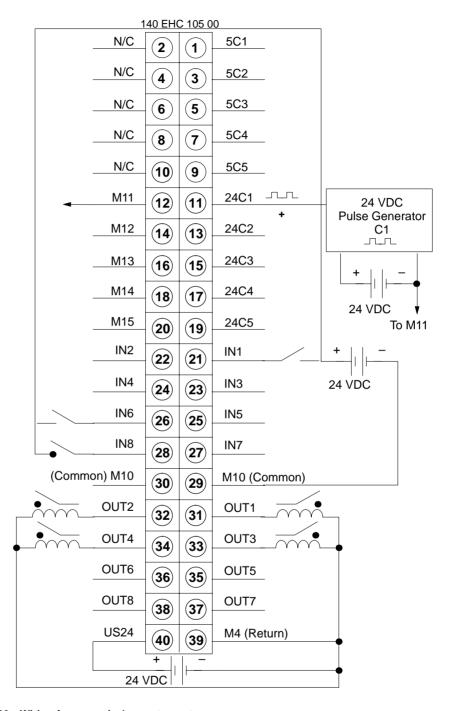

| 3.1.2     | Hardware Setup                                                                 |     |

| 3.1.3     | Schematic for Example 1, Event Counter                                         |     |

| 3.1.4     | Software Settings using Concept                                                |     |

| 3.1.4.1   | I / O Configuration (see above)                                                |     |

| 3.1.4.2   | Configuration of Final Signal Value and counter characteristics                |     |

| 3.1.5     | Software Settings using Modsoft                                                |     |

| 3.1.5.1   | I / O Configuration (see below)                                                | 51  |

| 3.1.5.2   | Configuration of Final Set Point Value and                                     |     |

|           | counter characteristics (see above)                                            | 53  |

| 3.1.6     | Start Counter 1                                                                |     |

| 3.1.7     | Example 1 Timing Diagram                                                       | 54  |

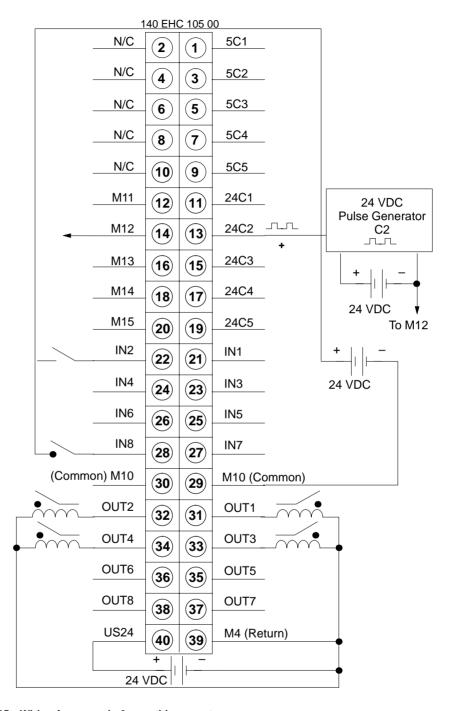

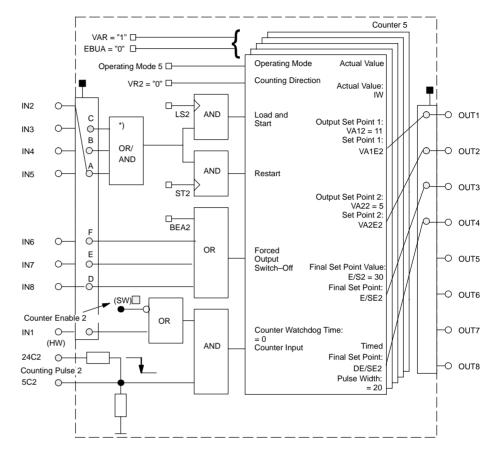

| 3.2       | Example 2: Repetitive Counter (Up)                                             |     |

|           | with serial setpoint output activation, counter 2, mode 5                      |     |

| 3.2.1     | Specifications                                                                 |     |

| 3.2.2     | Hardware Setup                                                                 |     |

| 3.2.3     | Schematic for Example 2, Repetitive Counter                                    |     |

| 3.2.4     | Software Settings using Concept                                                |     |

| 3.2.4.1   | I / O Configuration (see above)                                                | 58  |

| 3.2.4.2   | Configuration of Final Signal Value and                                        |     |

| 2.2.5     | counter characteristics (see above)                                            |     |

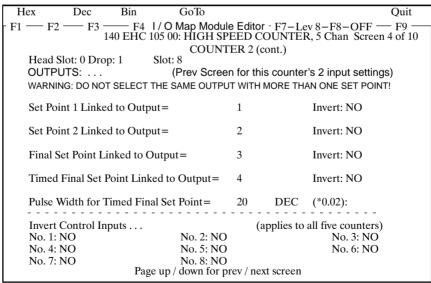

| 3.2.5     | Software Settings using Modsoft                                                |     |

| 3.2.5.1   | I / O Configuration (see above)                                                | וֹס |

| 3.2.5.2   | Configuration of Final Set Point Value and counter characteristics (see above) | 61  |

| 3.2.6     | Start Counter 2                                                                |     |

| 3.2.7     | Example 2 Timing Diagram                                                       |     |

| J.Z.1     | Example & Tilling Diagram                                                      | UU  |

IV Contents 000000.20

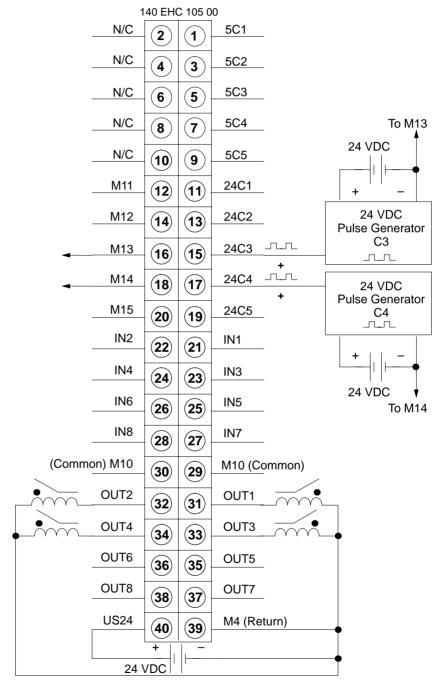

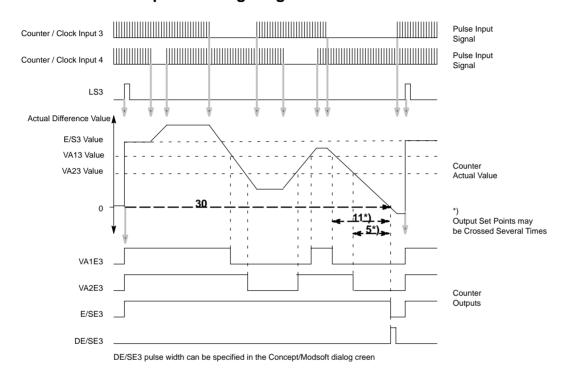

| 3.3         | Example 3: Differential Counter (Down) with       | •   |

|-------------|---------------------------------------------------|-----|

| 2.2.4       | parallel Set Point output activation, mode 3      |     |

| 3.3.1       | Specifications                                    |     |

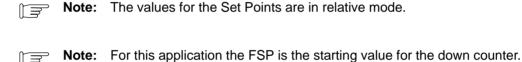

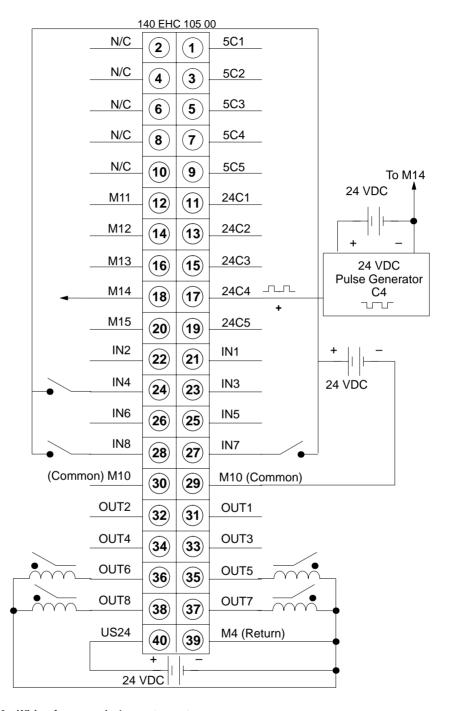

| 3.3.2       | Hardware Setup                                    |     |

| 3.3.3       | Schematic for Example 3, Differential Counter     |     |

| 3.3.4       | Software Settings using Concept                   |     |

| 3.3.4.1     | I / O Configuration Counter 3 (see above)         | 6   |

| 3.3.4.2     | Configuration of Final Signal Value and           | ~   |

| 0.05        | counter characteristics for Counter 3 (see above) |     |

| 3.3.5       | Software Settings using Modsoft                   |     |

| 3.3.5.1     | I / O Configuration (see above)                   | 7(  |

| 3.3.5.2     | Configuration of Final Set Point Value and        | _,  |

|             | counter characteristics (see above)               |     |

| 3.3.6       | Start Differential Counter                        |     |

| 3.3.7       | Example 3 Timing Diagram                          | 12  |

| 3.4         | Example 4: Event Counter (Up, Absolute) with      | _   |

|             | Timed Set Point output activation, mode A         |     |

| 3.4.1       | Specifications                                    |     |

| 3.4.2       | Hardware Setup                                    |     |

| 3.4.3       | Schematic for Example 4, Event Counter 4          |     |

| 3.4.4       | Software Settings using Concept                   |     |

| 3.4.4.1     | I / O Configuration (see above)                   | 76  |

| 3.4.4.2     | Configuration of Final Signal Value and           |     |

|             | counter characteristics (see above)               |     |

| 3.4.5       | Software Settings using Modsoft                   |     |

| 3.4.5.1     | I / O Configuration (see above)                   | 79  |

| 3.4.5.2     | Configuration of Final Set Point Value and        |     |

|             | counter characteristics (see above)               |     |

| 3.4.6       | Start Counter 4                                   | 80  |

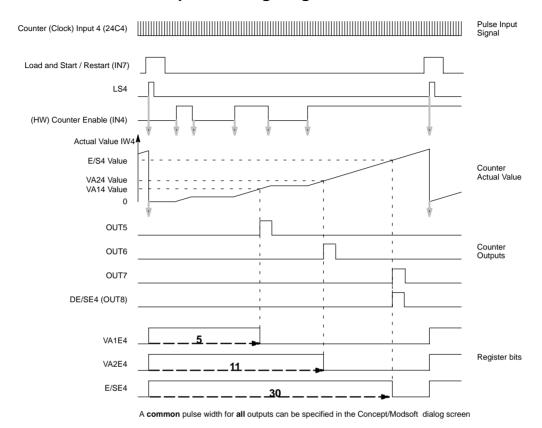

| 3.4.7       | Example 4 Timing Diagram                          | 8′  |

| Chapter 4   | Concept EHC 105 Derived Data Types                | 83  |

| Onaptor 4   | Concept End too Benveu Bata Types                 |     |

| Appendix A  | Module Description                                | 87  |

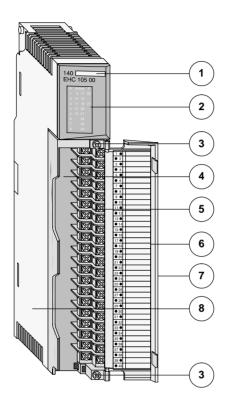

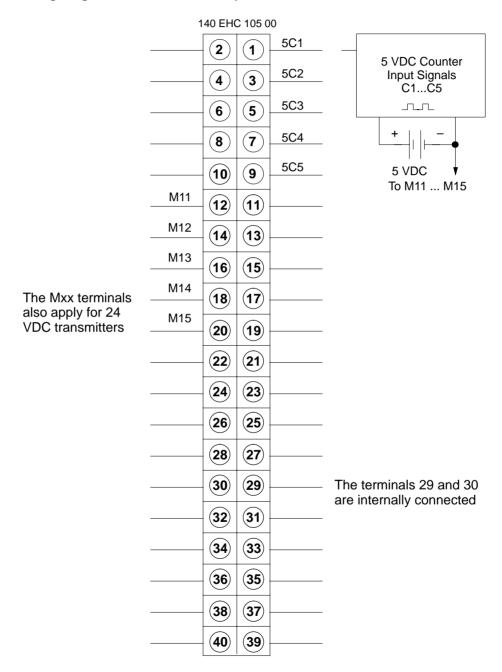

| 140 EHC 105 | 00 High-Speed Counter Module Description          | 89  |

|             | Index1                                            | 05  |

|             | Index                                             | 107 |

000000.20 Contents V

VI Contents

#### Symbols, Terminology, Abbreviations

Throughout this manual, the following visual aids highlight important and / or special information.

**Note:** Important, useful, or interesting information is shown as a note.

Caution: Cautions alert the reader of a possible hazard to the equipment or the product and then point out the propper procedure to avoid the hazard. Cautions also give the reader important instructions or strong suggestions to avert adverse consequences.

Warning: Warnings alert the reader of a possible hazard to personnel and then point out proper procedure to avoid the hazard.

**Expert:** This symbol is used when more detailed information is given, and is intended exclusively for experts (special training required). Skipping this information does not interfere with understanding the publication and does not restrict standard application of the product.

**Tip:** This symbol is used for Tips & Tricks.

**Path:** This symbol is a popup in the helptexts, this means you can click on it.

In software documentation this symbol tells you how to select the described menu commands and dialog boxes. The steps are always given starting from the main menu.

In EFB documentation (block libraries) this symbol tells you in which library and in which group you can find the described EFB.

Figures are given in the spelling corresponding to international practice and approved by SI (Système International d' Unités). I.e. a space between the thousands and a usage of a decimal point (e.g.: 12 345.67).

20 Foreword VII

#### **Declared Objectives**

This User Manual, including the EHC 105 module description, is to serve as an aid to fast counter configuration.

**Chapter 1** The operational characteristics of the EHC 105 are covered here.

**Chapter 2** This chapter describes module configuration and parameterization.

**Chapter 3** Four configuration examples are covered in this chapter.

**Chapter 4** In this chapter the EHC 105 derived data types are presented.

**Appendix A** This chapter contains the module description.

#### **Related Documents**

| Title                                                           | Örder Reference              |

|-----------------------------------------------------------------|------------------------------|

| Modicon TSX Quantum Automation Series, Hardware Reference Guide | 840 USE 100 00 (Version 5.0) |

| Modbus Plus Network, User's Manual                              | 890 USE 100 02               |

| Modicon Modlink, User's Guide                                   | GM-MLNK-001                  |

| Modicon IBM Host Based Devices, User's Guide                    | GM-HBDS-001                  |

| BM85 Modbus Plus Bridge / Multiplexer, User's Guide             | GM-BM85-001                  |

#### **Validity References**

The primary basis of this documentation is the EHC 105 module HW index level 12.02 and firmware version 2.0.7. The corresponding configuration software is Concept >= Release 2.0 or Modsoft >= Release 2.4.

**Note:** The latest information can be found in the Concept README.WRI file.

VIII Foreword 2

## **Chapter 1 Introduction to the EHC 105**

- The following topics will be reviewed:

- □ Introduction

- □ Operational Characteristics

- □ EHC 105 Counter Types

- ☐ State RAM Structure

- ☐ Monitoring Capabilities

- ☐ Start-Up Characteristics

#### 1.1 Introduction

#### 1.1.1 General

The EHC 105 module is a high–speed counter module for the Modicon TSX Quantum controller.

Counting frequencies of up to 100 kHz can be monitored, depending upon cable length, transmitter type and voltage refer to Modul description page 98, Table 14.

The EHC 105 includes 5 independent counters, each counter can be operated with either 5 or 24 VDC pulse input signals. The counters can be operated in the following operating modes:

| <ul> <li>Event counter, 32-bit, with four distinct operating r</li> </ul> | r distinct operating mod | oaes |

|---------------------------------------------------------------------------|--------------------------|------|

|---------------------------------------------------------------------------|--------------------------|------|

□ Differential counter, 32-bit, with two distinct operating modes

□ Repetitive counter, 16-bit

□ Rate counter, 32-bit, with two distinct operating modes

There are eight isolated, discrete inputs and eight isolated, discrete outputs (24 VDC level) available. These discrete I/Os can be assigned to the various signals of the individual counters.

This module is software configurable with Concept or Modsoft.

Configuration Information is transferred from the controller to the EHC 105 module only at controller start up or module hot swap.

Data transfer of the set point and actual values is exchanged every scan cycle.

The user program is processed in the controller.

The EHC105 module functions asynchronously with the controller, allowing fast response and control.

**Note:** Certain parameter defaults are assigned at module start–up, which among other things, assign specific functions to the discrete inputs (refer to page 34 Discrete I/O start–up assignments).

The EHC 105 is using with Modsoft or Concept.

#### 1.1.2 Using Concept and Modsoft

The following menu selection of terms for Concept and Modsoft are presented below and are described in this chapter.

#### **Menu Selection Terms:**

Concept 2.0 Modsoft 2.4

Output Switch-Off Output Switch-Off

Preceded Signal Set Point

Preceded Set Point

Final Signal

Final Signal Value

Final Set Point Value

Final Set Point Value

Dynamic Final Signal Timed Final Set Point Clock Watchdog Time Counter Watchdog Time

Clock Enable Counter Enable

Invert Clock Input Signal counts on:

–Pos. Transition–Neg. Transition

For configuration, Concept offers five dialog screens and Modsoft 10 dialog screens.

## 1.2 Operational Characteristics

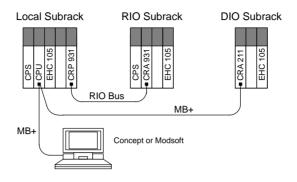

Figure 1 Typical hardware configuration

The counter module EHC105 needs 13 Out–register (4x...) and 12 In register (3x...) for configuration.

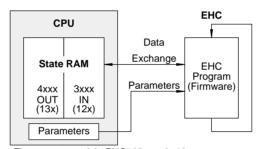

Figure 2 State RAM diagram as used by the counter

#### 1.2.1 EHC 105 Counter Channel Principles

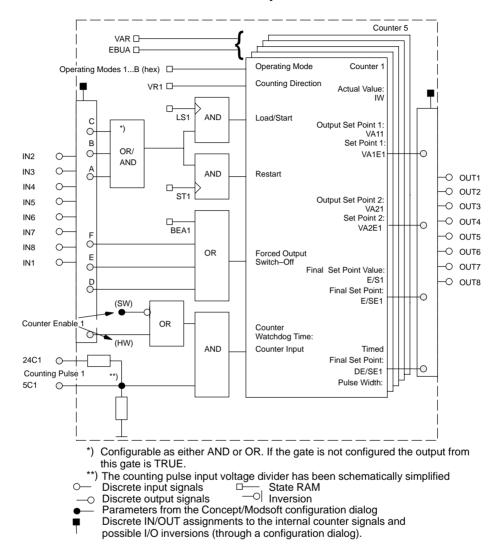

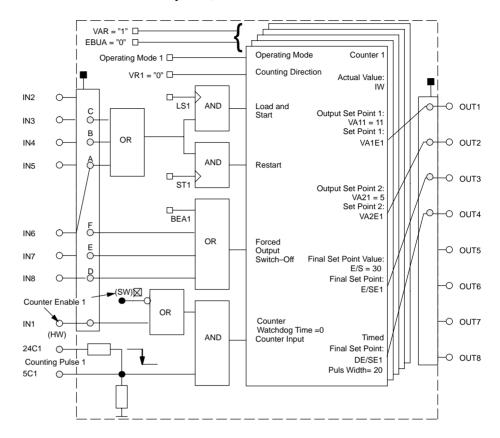

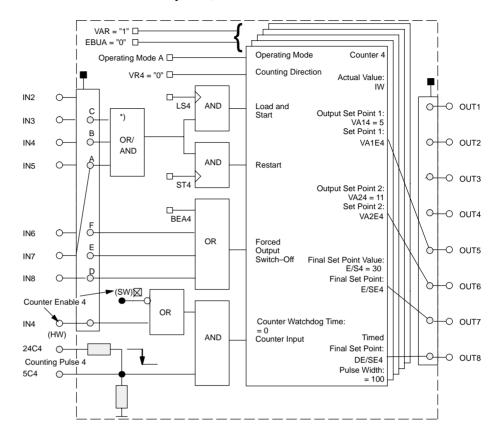

Figure 3 Counter block diagram (counter 1 is depicted)

#### 1.2.2 Description of the Individual Signals

| IN1 8:             | Discrete input signals which can be connected and individually inverted to the counter's control inputs .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>□ Each INx signal may be selected several times.</li> <li>□ Every input may be assigned the load/start, restart, or forced Output switch—off functions.</li> <li>□ Inputs can also be used as counter enable. However in this case the allocations are defined and may not be changed (i.e. IN1 is allocated counter 1, IN2 to counter 2, etc.).</li> <li>□ The response times (including firmware scans) are :</li> <li>□ 10 ms for inputs IN1IN6,</li> <li>□ 5 ms for the IN7 and IN8 inputs.</li> <li>□ Each discrete input can be inverted through the configuration dialogs.</li> </ul> |

|                    | <b>Note:</b> The default is "Not inverted". For default assignement refer to page 34, chapter 1.6 Start up characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 24Cx/5Cx (x = 15): | Discrete inputs for 24/5 VDC counting pulses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | <ul> <li>□ If the "Input Signal counts on:" is not selected ("Invert clock" in Concept 2.0) the counter will count on the "Neg. Transition".</li> <li>□ If the selection is made, the counter will count on the "Pos. Transition".</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

|                    | Note: The default is "Neg. Transition".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

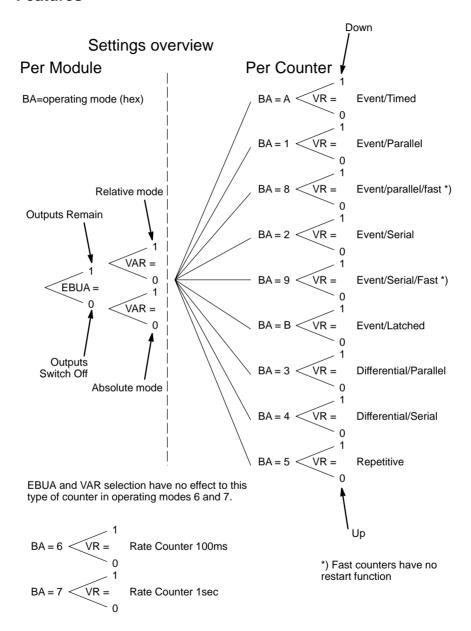

| VAR:               | is a bit within an output register (4x), which determines if the Output Set Points will be relative or absolute to Final Set Point Value for all 5 counters.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | <ul><li>□ "1" signal: Output Set Point is relative (to the Final Set Point Value)</li><li>□ "0" signal: Output Set Point is absolute.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | <b>Note:</b> Before configuration, the value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EBUA:              | Is an output register (4x) bit, which determines module switch-off behavior for all 5 counters when communication between the controller and EHC 105 is interrupted.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | <ul><li>□ "1" signal: The current output state is retained.</li><li>□ "0" signal: All used outputs are set to "0" level.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operating modes 1. | B:One of 11 possible operating modes that can be selected for each counter through a 4x register (Refer to page 31 ore 16).                                                                                                                                                                                                                                                         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <b>Note:</b> Before configuration mode is same as mode A. The remaining operating modes (0, C, D, E, F) are equal to the mode A.                                                                                                                                                                                                                                                    |

| VRx (x = 15):      | Is a bit within an output register (4x), which determines the counting direction of the associated counter. (See also Counting Direction page 14)                                                                                                                                                                                                                                   |

|                    | □ "1" signal: Down □ "0" signal: Up                                                                                                                                                                                                                                                                                                                                                 |

|                    | <b>Note:</b> Before configuration, the value is 0.                                                                                                                                                                                                                                                                                                                                  |

| LSx (x = 15):      | Load/start counter is a bit within an output register (4x), minimum pulse width: 3 ms. For more information refer to Figure 4 and Figure 5 on page 12 and 13 Relationship diagrams.                                                                                                                                                                                                 |

|                    | <b>Note:</b> Before configuration, the value is 0.                                                                                                                                                                                                                                                                                                                                  |

| BEAx (x = 15):     | Output Switch–Off is a bit within an output register (4x). The pulse must be at least 3ms width.  When BEAx is "1", it latches the current count in a buffer. While the counter continues to count, VA1Ex, VA2Ex and E/SEx are reset. This is also true for any assigned outputs Outx. For more information refer to Figure 4 and Figure 5 on page 12 and 13 Relationship diagrams. |

|                    | <b>Note:</b> Before configuration, the value is 0.                                                                                                                                                                                                                                                                                                                                  |

| STx (x = 15):      | Counter restart is a bit within an output register (4x), minimum pulse width: 3 ms.  STx signal releases buffer and counter value of equal current value.  For more information refer to Figure 4 and Figure 5 on page 12 and 13 Relationship diagrams.                                                                                                                             |

|                    | <b>Note:</b> Before configuration, the value is 0.                                                                                                                                                                                                                                                                                                                                  |

| Counter enable:  | These are two enable inputs which have the following functions:                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | $\square$ (SW) counter enable x (x = 15): software switch, that enables the counter and is activated from the Concept/Modsoft configuration screen. In Modsoft select the option as follow:                                                                                            |

|                  | □ "Use Input x for counter enable: Yes" : the (HW) counter enable is                                                                                                                                                                                                                   |

|                  | effective, □ "Use Input x for counter enable: No" : the counting pulse is always enabled.                                                                                                                                                                                              |

|                  | <b>Note:</b> The default is "Use Input x for counter enable: No".                                                                                                                                                                                                                      |

|                  | ☐ (HW) counter enable x (x = 15): Is a signal that enables the counter, if "Use Input x for counter enable:" is Yes.                                                                                                                                                                   |

|                  | Input channels for this function are predefined. IN1 is allocated to counter 1, IN2 is allocated to counter 2 etc.                                                                                                                                                                     |

|                  | <ul> <li>"1" signal: counter is enabled (Input not inverted).</li> <li>"0" signal: counter is disabled (Input not inverted).</li> </ul>                                                                                                                                                |

|                  | o signal. counter is disabled (input not inverted).                                                                                                                                                                                                                                    |

|                  | <b>Note:</b> The default: Input is not selectable for counter enable.                                                                                                                                                                                                                  |

| $\triangle$      | Caution: The pulse counting begins after the first complete pulse following the counter enable signal. Accordingly, after counting pulse disable, the next counting pulse will still be registered. As a result during each count cycle (enable / disable), one pulse will be missing. |

| Counter Watchdog | Timer: This timer monitors incoming pulses and can be enabled throught the Concept / Modsoft dialog screen:                                                                                                                                                                            |

|                  | □ Value 0: no monitoring □ Values 1255: (x 0.1) sec                                                                                                                                                                                                                                    |

|                  | Note: The default is value 0.                                                                                                                                                                                                                                                          |

| VA1x (x = 15):   | Is the first Output Set Point and can be configured through the Concept / Modsoft dialog screen.  Value range: 0(2 exp31) –1                                                                                                                                                           |

**Note:** The default is value 0.

If relative Output Set Point mode is selected, output Set Point Values are

relative to the Final Set Point Value.

Requirement for that: E/S > VA1 >= VA2 >= 0.

If absolute Output Set Point mode is selected, this value is absolute.

Requirements for that: E/S > VA2 >= VA1 >= 0.

**VA1Ex (x = 1...5):** Is a bit within an input register (3x...).

☐ This may be assigned through the Concept / Modsoft dialog screen to any of the discrete outputs OUT1...OUT8.

**Note:** Before configuration, the value is 0. For default assignement refer to page 34, chapter 1.6 Start up characteristics.

VA2x (x = 1...5): Is the second Output Set Point and can be configured through the the Concept / Modsoft dialog screens.

Value range: 0...(2 exp31) −1

Note: The default is value 0.

If relative Output Set Point mode is selected, output Set Point Values are relative to the Final Set Point Value.

Requirement for that: E/S > VA1 >= VA2 >= 0.

If absolute Output Set Point mode is selected, this value is absolute.

Requirements for that: E/S > VA2 >= VA1 >= 0.

**VA2Ex** (x = 1...5): Is a bit within an input register (3x...).

☐ This may be assigned through the Concept / Modsoft dialog screen to any of the discrete outputs OUT1...OUT8.

Note: The default assignement refer to page 34, chapter 1.6 Start up characteristics.

**E/Sx (x = 1...5):** Is an output register (4x...) in which the counter's final (up counter) or inital (down counter) is entered.

Value range: 0...(2 exp31) −1

Note: Before configuration, the value is 0.

**E/SEx (x = 1...5):** Final Set Point is a bit within an input register (3x...).

|                  | ☐ This may be assigned through the Concept / Modsoft dialog screen to any of the discrete outputs OUT1OUT8.                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <b>Note:</b> Before configuration, the value is 0. For default assignement refer to page 34, chapter1.6 Start up characteristics.                                                                  |

| DE/SEx (x = 15): | The Timed Final Set Point, settable through the Concept / Modsoft dialog screen:                                                                                                                   |

|                  | ☐ This may be assigned through the Concept / Modsoft dialog screen to any of the discrete outputs OUT1OUT8.                                                                                        |

|                  | <b>Note:</b> Before configuration, the value is 0. The default assignement is: No assignement.                                                                                                     |

| Pulse width:     | This defines the length of the Timed Final Set Point pulse. In addition, in operating mode A, this defines the time for all associated outputs.                                                    |

|                  | □ Value 0: output DE/SEx is disabled □ Values 1255: (x 0.02) sec.                                                                                                                                  |

|                  | Note: The default value is 0.                                                                                                                                                                      |

| STOP             | Warning: If in operating mode A, this value equal "0" there will be no outputs.                                                                                                                    |

| OUT18:           | Discrete output signals, which can be assigned and individually inverted to the counter outputs VA1E (Set Point 1), VA2E (Set Point 2), E/SE (Final Set Point), and DE/SE (Timed Final Set Point). |

|                  | <b>Note:</b> The default: outputs are not inverted. The default assignment refer to page 34, chapter1.6 Start up characteristics.                                                                  |

|                  |                                                                                                                                                                                                    |

one Set Point. Even if Modsoft allowed you to do that, such multiple use is prohibited. Such double assignments lead to unpredictable process states, and are particularly difficult to diagnose.

Warning: Do not select the same output OUT1 ... OUT8 with more than

#### 1.2.3 Output Set Point Mode (Absolute, Relative)

The Output Set Point is configured once for all module counters.

The module operates in absolute or relative Output Set Point Mode.

#### 1.2.3.1 Absolute Output Set Point Mode

In this mode, the value entered in the Concept / Modsoft screen is the actual Output Set Point.

#### 1.2.3.2 Relative Output Set Point Mode

In this mode, the Output Set Point is the difference between the entered value in the Concept / Modsoft screen and the Final Set Point Value.

#### 1.2.4 Start and Stop Function Priority Rankings

The prioritazing of signals to start or stop a counter is as follow:

- **Priority 1** Forced Output Switch–Off, active for BEAx = "1" (state RAM) OR one of the configured discrete inputs as "1".

- **Priority 2** Load/start counter, active for LSx = "1" (state RAM) AND a TRUE evaluation of the configured discrete inputs.

- **Priority 3** Restart counter, active for STx = "1" (state RAM) AND a TRUE evaluation of the configured discrete inputs.

**Note:** The user program commands are necessary for starting and restarting of the counting procedures. Setting of the corresponding discrete inputs is also required. When no discrete input is assigned to the commands through "Load/Start and Restart", the counting procedure is initiated through the output status word (4x...) bits LSx resp. STx.

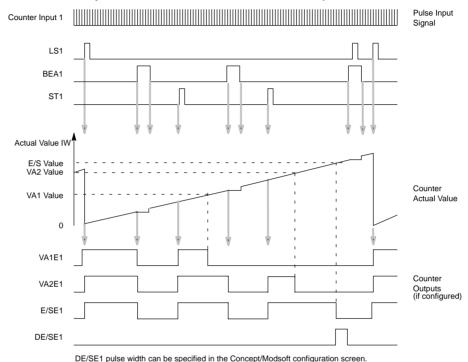

#### 1.2.4.1 Relationship Diagrams of LS1, ST1, and BEA1 for Counter 1

Without hardware input configuration (Load/Start, Restart, Output-Switch-Off and Counter Enable).

Figure 4 Counter 1 diagram as event counter, parallel, absolute, output function non inverted and counting up

LS1: With the rising edge from LS1, the actual counting value is set to 0. The outputs VA1E1, VA2E1 and E/SE1 are set to "1" signal for the operation mode 1 ... 5 and 8,9 or to "0" signal for operation mode A and B.

BEA1 / ST1: With a "1" signal at BEA1 the actual value will latch; the counting continues in an internal memory of the module. Is there on BEA1 a "0" signal the counting of the actual value continues with the current contents of the memory. Is there on ST1 a rising edge the outputs switche on depended from the actuale value.

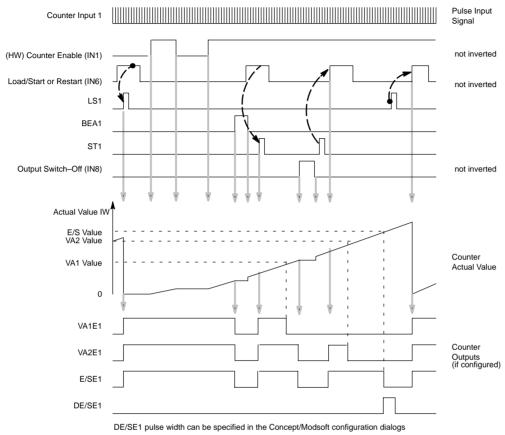

## With hardware input configuration (Load/Start, Restart, Output-Switch-Off and Counter Enable).

Figure 5 Counter 1 diagram as event counter, parallel, absolute, with output function non inverted and counting up

**Note:** The discrete input evaluation for "Load/Start or Restart" is AND'ed with the LSx resp. STx signal. The LSx and STx signals operate edge—controlled.

**Note:** The "Output Switch-Off" discrete inputs have the same function as the BEAx bit.

The AND condition is true should there have been no configuration carried out for "Load/Start or Restart"; the LSx and STx bits then function alone.

If the discrete input is not inverted, the High signal is active (see figure above). If discrete input is inverted, the Low signal is active. LSx and STx bit are always active with the rising ege, it can not be inverted.

BEAx is always active with the High signal, it can not be inverted. An active BEA signal set all inverted outputs to a High signal. If the Outputs are inverted, the state from the signals VA1Ex, VA2Ex and E/SEx will not inverted.

#### 1.2.5 Counting Direction Determination

The individual counters can function as bidirectional counters, counting up or down. The counting direction is specified by output status word (4x...) bit VR.

- $\square$  VRx = "0": Up-counter, starting with 0, stop at final value E/S.

- $\square$  VRx = "1": Down-counter, starting at initial value E/S, stop at 0

**Note:** Do not change the value of the VRx bit during operation of the counter. If the value changes, the associated outputs of the counter will be switched off.

## 1.2.6 Overview and Relationships of Counter Functionality Features

Figure 6 Possible counter settings

#### 1.3 EHC 105 Counter Types

The EHC 105 module can operate as:

| ☐ Event counter (with and without fast Final Set Point |

|--------------------------------------------------------|

| ☐ Event counter with Timed or latched outputs          |

| □ Differential counter (without fast Final Set Point)  |

| □ Repetitive counter (with fast Final Set Point)       |

| □ Rate counter                                         |

The selection of the various counter types takes place through the operating mode selections in state RAM. Every counter type can count up and down. Output Set Point Mode can be set to be relative (to the Final Set Point Value) or absolute.

**Note:** For an active counter, any change of the operating mode or counting direction, switch–off behavior, or type of Set Point triggers an Output Switch–Off. A change of the operating mode accompanied by load/start is not possible. (The setting of the load / start bit after changing the operation mode must be done in the next scan cycle.)

**Note:** Discrete Output Signal Response Times: Without fast Final Set Point: typically 3 ms. With fast Final Set Point: typically 0.5 ms.

Table 1 Counter Operating modes

| Value (hex)    | Meaning                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Event counter with parallel Set Point activations                                                                                                               |

| 2              | Event counter with serial Set Point activations                                                                                                                 |

| 3              | Differential counter with parallel Set Point activations (only applies to counters 1 and 3, the Set Point and actual values of counters 2 resp. 4 are inactive) |

| 4              | Differential counter with serial Set Point activations (only applies to counters 1 and 3, the Set Point and actual values of counters 2 resp. 4 are inactive)   |

| 5              | Repetitive counter                                                                                                                                              |

| 6              | Rate counter, gate time t = 100 ms                                                                                                                              |

| 7              | Rate counter, gate time t = 1 s                                                                                                                                 |

| 8              | Event counter with parallel Set Point activations and fast Final Set Point                                                                                      |

| 9              | Event counter with serial Set Point activations and fast Final Set Point                                                                                        |

| A<br>(default) | Event counter with timed "on" outputs, the pulse width setting holds for all employed outputs.                                                                  |

Table 1 Counter Operating modes

| Value (hex)   | Meaning                                       |

|---------------|-----------------------------------------------|

| В             | Event counter with latched Set Point outputs. |

| 0, C, D, E, F | as operating mode A                           |

#### 1.3.1 The Event Counter

The event counter is a gate—controlled, bidirectional counter with two or less Set Points, a Final Set Point and a Timed Final Set Point. It utilizes six different operating modes. See also Table 5 on page 31.

| □ Operating mode A: with adjustable "time on" outputs                 |

|-----------------------------------------------------------------------|

| ☐ The pulse width configuration applies the same value to all counter |

| outputs. Outputs are at "0" signal on start.                          |

| ☐ Operating mode 1: with parallel Output Set Point activation         |

| □ Operating mode 2: with serial Output Set Point activation           |

| □ Operating mode 8: with parallel Output Set Point activation and     |

| fast Final Set Point                                                  |

| ☐ Operating mode 9: with serial Output Set Point activation and       |

| fast Final Set Point                                                  |

| □ Operating mode B: with latched Set Point activation                 |

| Outputs are at "0" signal on start.                                   |

The value range for all operating modes amounts to: 0...(2 exp 31) - 1, except the operating mode 5 is 0...(2 exp 16) - 1.

## 1.3.1.1 Operating modes 1 and 8 (Event counter with relative Output Set Point Value and parallel Set Point activation)

Figure 7 Counting up (VR = 0)

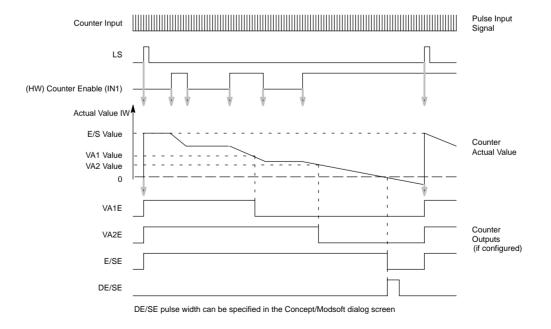

Figure 8 Counting down (VR = 1)

## 1.3.1.2 Operating modes 2 and 9 (Event counter with relative Output Set Point Value and serial Set Point activation)

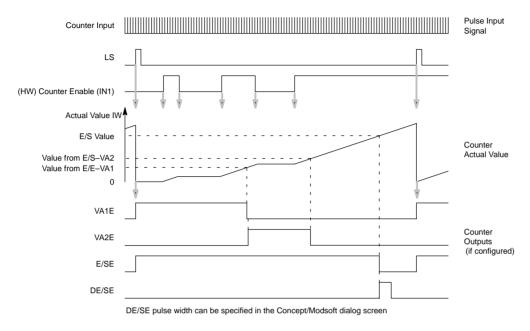

Figure 9 Counting up (VR = 0)

Figure 7 to Figure 9 Event counter with relative and parallel and serial Set Point activation are typical time diagrams.

That do no take into account the following signals:

- □ BEAx Further information you will find on page 12

- ☐ STx Further information you will find on page 12

Note: STx has no function in the operating modes 8 and 9.

## 1.3.1.3 Operation mode A (Event counter with absolute Output Set Point Value and timed output activation)

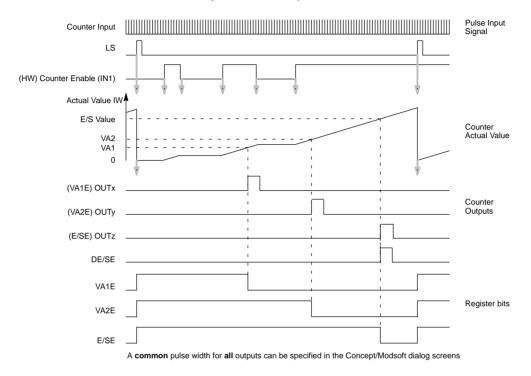

Figure 10 Counting up (VR = "0")

**Note:** The activation of the discrete outputs are different from the activation of the register bits.

## 1.3.1.4 Operation-mode B (Event counter with absolute Output Set Point Value and latched output activation)

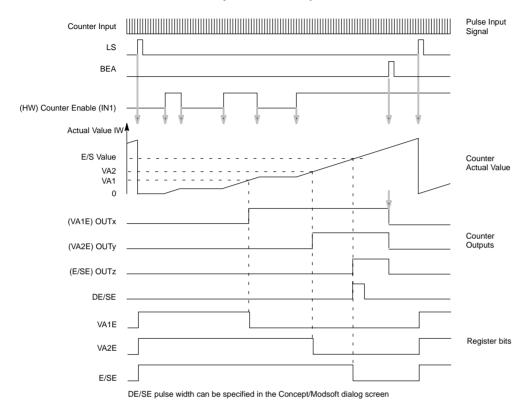

Figure 11 Counting up (VR = 0)

**Note:** The activation of the discrete outputs are different from the activation of the register bits.

#### 1.3.2 The Differential Counter

The differential counter is a gate—controlled counter with up to two Output Set Points, a Final Set Point and a Timed Final Set Point. A differential counter consists of two counter channels and measures the difference of each of their pulses. It is equipped with two different operating modes:

| □ Operating mode 3: with parallel Set Point activation                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| □ Operating mode 4: with serial Set Point activation                                                                                                                                                    |

| Counter 1 (clockwise) and 2 (counterclockwise) form a differential counter 1, while counter 3 (clockwise) and 4 (counterclockwise) form a differential counter 2. This configuration cannot be changed. |

| The counting value is determined from the difference of the two counters.                                                                                                                               |

| Differential counter configuration, control and evaluation is done through the parameters and values of the first counter with the exception of the counter input.                                      |

| The configuration for the respective second counter must be performed separately. The parameter choices (from the Modsoft / Concept dialog screen) are:                                                 |

| □ Invert Counter Input / Input Signal counts on.                                                                                                                                                        |

| ☐ Use Input for Counter enable / Input for Counter enable.                                                                                                                                              |

| <b>Note:</b> A fast Final Set Point cannot be set for differential counters. If a counte is disabled, counter time monitoring is suspended.                                                             |

| ☐ The value ranges are as follows:                                                                                                                                                                      |

| □ Set Point values: 0(2 exp 30) −1 □ Actual values: −(2 exp 30)(2 exp 30) −1                                                                                                                            |

**Note:** The value range allows the differential counter to also be used for continuous monitoring.

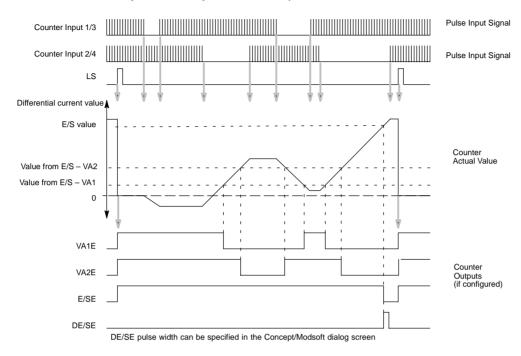

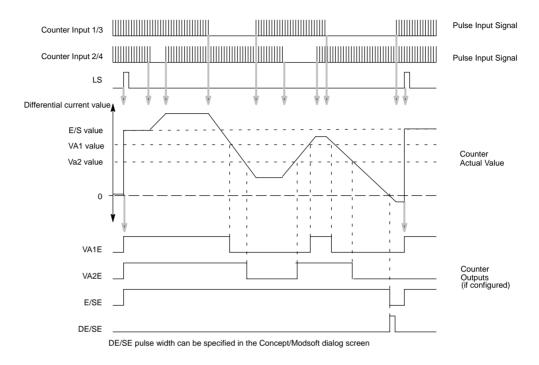

## 1.3.2.1 Operating mode 3 (Differential counter with relative Output Set Point Value and parallel output activation)

Figure 12 Differential counter with parallel output activation counts up (VR = 0)

## Continuation Operating Mode 3 (Differential counter with relative Output Set Point Value and parallel output activation)

Figure 13 Differntial counter with parallel output activation counts down (VR = 1)

Figure 12 and Figure 13 "Differential counter with parallel set–point cutoffs (VR = 0)" are typical timing diagram that do not take into account the following signals:

- ☐ BEAx Further information you will find on page 12

- □ STx Further information you will find on page 12

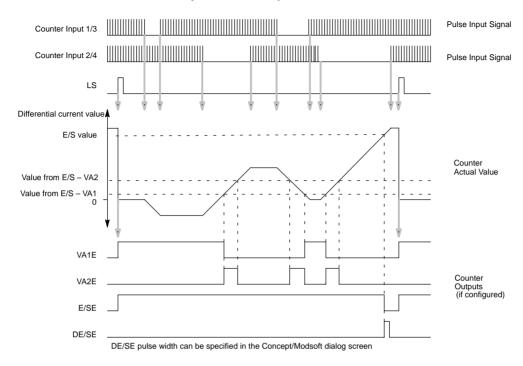

## 1.3.2.2 Operating mode 4 (Differential counter with relative Output Set Point Value and serial output activation)

Figure 14 Differential counter with serial output activation counts up (VR = 0)

Figure 14 "Differential counter with serial set–point cutoffs" is a typical timing diagram that do not take into the following signals:

- □ BEAxFurther information you will find on page 12

- □ STxFurther information you will find on page 12

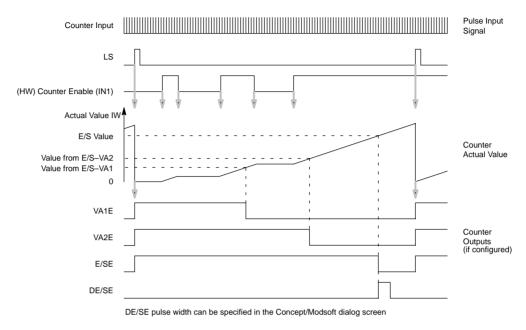

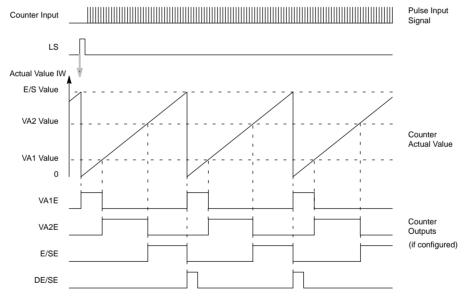

#### 1.3.3 The Repetitive Counter (Operating mode 5)

The repetitive counter is an up / down counter with up to two Output Set Points, a fast Final Set Point, which acts as a third Set Point and a Timed Final Set Point.

☐ Operating Mode 5: with serial output activation

As a repetitive counter, every time the Final Set Point value is reached, the following restrictions apply:

- $\Box$  E/Sx values are limited to the value ranges 0...(2 exp 16) -1.

- ☐ The Final Set Point value cannot be changed when the counter is active. BEA must be set in advance.

- ☐ The Final Set Point Value must be equal or greather than 2.

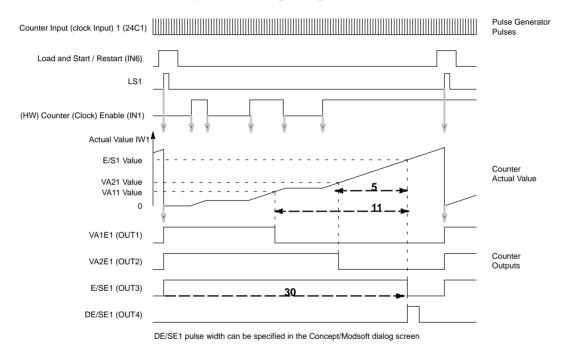

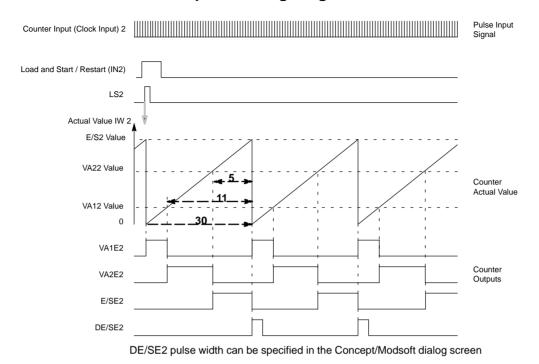

DE/SE pulse width can be specified in the Concept/Modsoft dialog screen

Figure 15 Repetitive counter with serial output activation

Figure 15 "Repetitive counter" is a typical timing diagram that does not take into account the following signal:

- ☐ BEAxFurther information you will find on page 12

- □ STx has no effect in this operating mode refer to page 12 for further information

#### 1.3.4 The Rate Counter (Operating mode 6 or 7)

The rate counter counts the number of pulses per unit time. A unit time is specified with the choice of the operating modes 6 or 7. The read value is then saved as the actual value.

The determined actual value thus represents the pulse count per unit time, and can be used to determine velocities, flow rates, or even revolutions.

Inputs and outputs are not processed in this counter type.

THe Watchdog timer function is not supported.

There are two operating modes for the rate counter. These differ only in the prescribed internal gate time.

- □ Operating mode 6: The gate time t amounts to 100 ms

- ☐ Operating mode 7: The gate time t amounts to 1 s

#### 1.4 State RAM Structure

#### 1.4.1 Input Structure

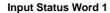

Table 2 State RAM input structure (EHC 105 -> CPU ), word addressing

| 3x Registers | Relative Address |           | Content             |

|--------------|------------------|-----------|---------------------|

| 3x           | 000              |           | Input Status Word 1 |

| 3x+1         | 001              |           | Input Status Word 2 |

| 3x+2         | 002              | Low Word  | Counter 1           |

| 3x+3         |                  | High Word | Actual Value        |

| 3x+4         | 004              | Low Word  | Counter 2           |

| 3x+5         |                  | High Word | Actual Value        |

| 3x+6         | 006              | Low Word  | Counter 3           |

| 3x+7         |                  | High Word | Actual Value        |

| 3x+8         | 008              | Low Word  | Counter 4           |

| 3x+9         |                  | High Word | Actual Value        |

| 3x+10        | 010              | Low Word  | Counter 5           |

| 3x+11        |                  | High Word | Actual Value        |

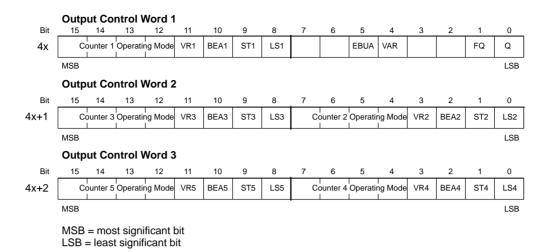

#### Quantum local drop:

The relative address relates to the Concept configuration "In Ref" address, refer to Configuration Steps in chapter 2.2.2.1, page 39.

#### Modsoft Configuration:

The relative address relates to the Modsoft configuration "Input Ref" address, refer to Configuration Steps, chapter 2.2.3.1, page 42.

**Note:** Counter actual values are shown as decimal values: in Concept as Dec (signed 32–bit); in Modsoft as Long Dec (unsigned 32–bit) for CPU Exec 2.0 and greather. This means that negative values can not be displayed correctly.

#### **Input Status Word 2**

MSB = most significant bit LSB = least significant bit

Table 3 Input status word signal explanations

| Signal              | Va-<br>lue | Meaning                                                                     |

|---------------------|------------|-----------------------------------------------------------------------------|

| Input Status        | Word 1     |                                                                             |

| ERRx                | 1          | Error in counter x (specified by Indicate, i.e. bit 5 in status word 1)     |

| INDICATE            | 0          | Counter overflow (actual value > 2 exp (16), 2 exp (30) resp. 2 exp (31)-1) |

|                     | 1          | Counting pulse error (counter timeout value expired)                        |

| SC                  | 1          | Discrete output short circuit or overload                                   |

| US24                | 1          | External power failure (discrete outputs)                                   |

| E/SEx               | 1          | Final set point signal on counter x is 1 Signal                             |

| Input Status Word 2 |            |                                                                             |

| VA1Ex               | 1          | First Set Point signal on counter x is a 1 Signal                           |

| VA2Ex               | 1          | Second Set Point signal on counter x is a 1 Signal                          |

**Note:** Output inversions (E/SEx, VA1Ex, VA2Ex) are not used on the corresponding bits in status words 1 and 2.

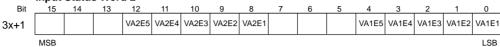

#### 1.4.2 Output Structure

Table 4 State RAM output structure (CPU -> EHC 105), word addressing

| 4x Regi-<br>ster | Relative<br>Address |           |               | Content                                   |

|------------------|---------------------|-----------|---------------|-------------------------------------------|

| 4x               | 000                 |           |               | Output Control Word 1                     |

| 4x+1             | 001                 |           |               | Output Control Word 2                     |

| 4x+2             | 002                 |           |               | Output Control Word 3                     |

|                  |                     |           | Counter 1     |                                           |

| 4x+3             | 003                 | Low Word  | Stop value    | for VR1 = "0", Final Set Point Value E/S1 |

| 4x+4             |                     | High Word | Initial value | for VR1 = "1", Final Set Point Value E/S1 |

|                  |                     |           | Counter 2     |                                           |

| 4x+5             | 005                 | Low Word  | Stop value    | for VR2 = "0", Final Set Point Value E/S2 |

| 4x+6             |                     | High Word | Initial value | for VR2 = "1", Final Set Point Value E/S2 |

|                  |                     |           | Counter 3     |                                           |

| 4x+7             | 007                 | Low Word  | Stop value    | for VR3 = "0", Final Set Point Value E/S3 |

| 4x+8             |                     | High Word | Initial value | for VR3 = "1", Final Set Point Value E/S3 |

|                  |                     |           | Counter 4     |                                           |

| 4x+9             | 009                 | Low Word  | Stop value    | for VR4 = "0", Final Set Point Value E/S4 |

| 4x+10            |                     | High Word | Initial value | for VR4 = "1", Final Set Point Value E/S4 |

|                  |                     |           | Counter 5     |                                           |

| 4x+11            | 011                 | Low Word  | Stop value    | for VR5 = "0", Final Set Point Value E/S5 |

| 4x+12            |                     | High Word | Initial value | for VR5 = "1", Final Set Point Value E/S5 |

Quantum local drop: The relative address relates to the Concept configuration "Out Ref" address, refer to (Configuration Steps chapter 2.2.2.1, page 39).

Modsoft Configuration: The relative address relates to the Modsoft configuration "Output Ref" address, (refer to Configuration Steps, chapter 2.2.3.1, page 42).

Table 5 Output control word signal explanations

| Signal                                       | Value (hex)    | Meaning                                                                                                                                                         |

|----------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter x Opera-<br>ting Mode                | 1              | Event counter with parallel Set Point activations                                                                                                               |

| 2 Eve                                        |                | Event counter with serial Set Point activations                                                                                                                 |

|                                              | 3              | Differential counter with parallel Set Point activations (only applies to counters 1 and 3, the Set Point and actual values of counters 2 resp. 4 are inactive) |

|                                              | 4              | Differential counter with serial Set Point activations (only applies to counters 1 and 3, the Set Point and actual values of counters 2 resp. 4 are inactive)   |

|                                              | 5              | Repetitive counter                                                                                                                                              |

|                                              | 6              | Rate counter, gate time t = 100 ms                                                                                                                              |

|                                              | 7              | Rate counter, gate time t = 1 s                                                                                                                                 |

| 8 Event counter with paralle Final Set Point |                | Event counter with parallel Set Point activations and fast Final Set Point                                                                                      |

|                                              | 9              | Event counter with serial Set Point activations and fast Final Set Point                                                                                        |

|                                              | A<br>(default) | Event counter with timed "on" outputs, the pulse width setting holds for all employed outputs.                                                                  |

|                                              | В              | Event counter with latched Set Point outputs.                                                                                                                   |

|                                              | 0, C, D, E, F  | as operating modes A                                                                                                                                            |

| VRx                                          | 0              | Counter x counts up                                                                                                                                             |

|                                              | 1              | Counter x counts down                                                                                                                                           |

| BEAx                                         | 1              | Counter x Output Switch-Off                                                                                                                                     |

| STx                                          | 1              | Counter x restart (controlled by rising edge)                                                                                                                   |

| LSx                                          | 1              | Counter x load/start (controlled by rising edge)                                                                                                                |

| EBUA                                         | 1              | Outputs retain their current state on communication errors                                                                                                      |

|                                              | 0              | Outputs go to "0" signal on communication errors                                                                                                                |

Table 5 Output control word signal explanations

| Signal | Value (hex)                                          | Meaning                                                                                                                                                                                                    |

|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAR    | 1 Output Set Points (values) are relative for all co |                                                                                                                                                                                                            |

|        | 0                                                    | Output Set Points (values) are absolute for all counters                                                                                                                                                   |

| Q      | 1                                                    | Acknowledgement for all counter channels after an output short circuit fault signal (SC). (The red LED (F) extinguishes).                                                                                  |

| FQ     | 1                                                    | Acknowledgement after power failure and counter errors (ERR1ERR5 and Indicate). (The red LED (F) extinguishes). If several errors are present, they must be acknowledged individually one after the other. |

Caution: If the counter's operating mode, counting direction, switch-off behavior, or type of Set Point are changed while the counter's output signals are active, the output will be deactivated and the new changes will take effect.

#### 1.5 Monitoring Capabilities

#### 1.5.1 Input Signal Monitoring

The EHC 105 can monitor the presence or absence of incoming signals. To activate signal monitoring, it is necessary to state a value between 1 and 255 in the Concept / Modsoft dialog screen for "Clock/Counter Watchdog Time". This fixes the counter's watchdog timers within the limits from 100 ms to 25.5 s. No monitoring is performed for 0 values.

If a pulse is not detected at the respective input of a running counter within the declared timeout interval, then the transmitter error flag (INDICATE) is changed to "1" and the corresponding error bit (ERR) is on, triggering a Forced Output Switch–Off and "F" LED is ON.

Counting pulse monitoring for the respective counter occurs when the counting pulse is enabled and the counter is running. The prerequisite is the specification of a watchdog timer: (Refer to page 6ff)

**Note:** Count pulse monitoring is not supported in operating modes 6 and 7. Refer to chapter 1.3.2, page 22 differential counters.

#### 1.5.2 Quantum System Bus Monitoring

A "system active" signal is activated on the Quantum system bus. If the CPU fails, all outputs are set accordingly and the green ACTIVE status LED turns off.

The status of the outputs in the event of a communication failure between the controller and the EHC 105 can be selected through the EBUA output register bit (4x...).

□ "1" signal: The current output state is retained.□ "0" signal: All employed outputs are set to "0" level.

#### 1.5.3 US24 Power Monitoring

If the external 24VDC power supply fails during operation, the green "P" LED turns off and is shown in the module status byte and the red "F" LED turns on. If the power goes on again, the "P" LED turns on and the "F" LED turns off. An Output Switch–Off is not triggered for a running counter. The discrete output (OUT1...OUT8) status displays (1▶ to 8▶) turn off (independent from the defined output logic).

#### 1.6 EHC 105 Start-Up Characteristics

At EHC 105 start—up, all actual values are cleared to 0, outputs are deactivated (i.e. VA1E=VA2E=E/SE ="0") and the counters are defaulted to up—event counters, with absolute Output Set Point Values (VAR = "0") and outputs in timed control mode (operating mode A).

Outputs are set to "0" (EBUA = "0") on controller communications failure with the EHC105.

By default, all counters are enabled.

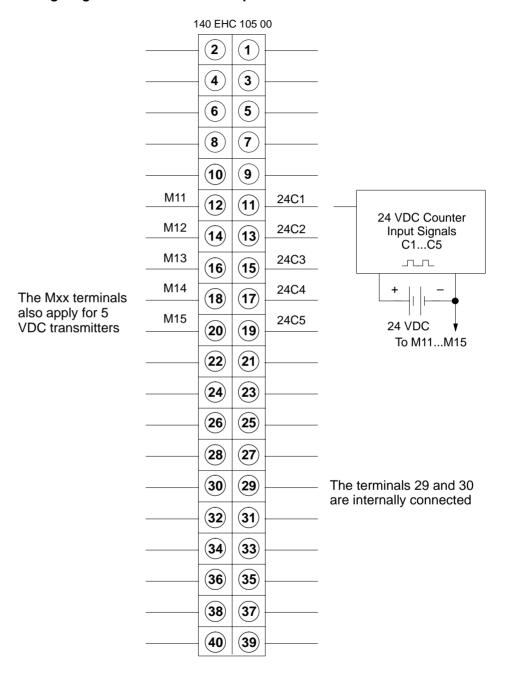

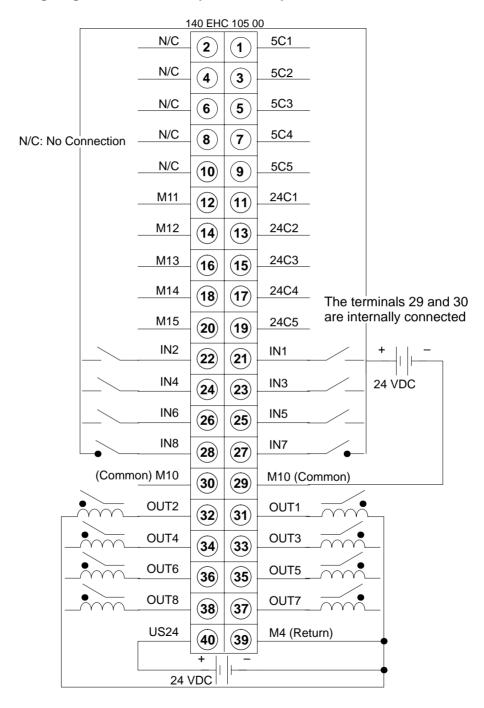

Table 6 Start-up assignments for discrete I/O

| Counter Input/Output     | Discrete Signal | Pin Assignments |

|--------------------------|-----------------|-----------------|

| Counter 1                | •               | •               |

| LS1 (Load and Start)     | IN1             | 21              |

| ST1 (Restart)            | IN1             | 21              |

| BEA1 (Output Switch-Off) | IN6             | 26              |

| Counting Pulse 1         | 5C1/24C1        | 1/11            |

| VA2E1                    | OUT6            | 36              |

| E/SE1                    | OUT1            | 31              |

| Counter 2                |                 | •               |

| LS2 (Load and Start)     | IN2             | 22              |

| ST2 (Restart)            | IN2             | 22              |

| Counting Pulse 2         | 5C2/24C2        | 3/13            |

| E/SE2                    | OUT2            | 32              |

| Counter 3                |                 |                 |

| LS3 (Load and Start)     | IN3             | 23              |

| ST3 (Restart)            | IN3             | 23              |

| BEA3                     | IN7             | 27              |

| Counting Pulse 3         | 5C3/24C3        | 5/15            |

| VA2E3                    | OUT7            | 37              |

| E/SE3                    | OUT3            | 33              |

| Counter 4                |                 |                 |

| LS4 (Load and Start)     | IN4             | 24              |

| ST4 (Restart)            | IN4             | 24              |

| Counting Pulse 4         | 5C4/24C4        | 7/17            |

| E/SE4                    | OUT4            | 34              |

Table 6 Start-up assignments for discrete I/O

| Counter Input/Output | Discrete Signal | Pin Assignments |

|----------------------|-----------------|-----------------|

| Counter 5            |                 |                 |

| LS5 (Load and Start) | IN5             | 25              |

| ST5 (Restart)        | IN5             | 25              |

| Counting Pulse 5     | 5C5/24C5        | 9/19            |

| BEA5                 | IN8             | 28              |

| VA2E5                | OUT8            | 38              |

| E/SE5                | OUT5            | 35              |

# **Chapter 2 Configuration**

- ☐ Hardware and Software Prerequisites

- □ Configuration Steps

20

Configuration

37

#### 2.1 Hardware and Software Prerequisites

| □ PC for Concept / Modsoft                                                     |       |

|--------------------------------------------------------------------------------|-------|

| $\square$ Software package: Concept $\ge$ version 2.0 or Modsoft $\ge$ version | n 2.4 |

| □ CPU EXEC ≥ version 2.0                                                       |       |

| □ Quantum System with any CPU refer to "Quantum Reference G (840 USE 100 00)"  | iuide |

**Note:** Althought, this module is also supported with Modsoft 2.32, version 2.4 or greater is required. The screens, described in this document come from version 2.4.

This module is also supported with Concept 1.13, but we recommand to use version 2.0 or greater. The screens, described in this document come from version 2.0.

#### 2.2 Configuration Steps

The steps necessary for configuration are presented here. Where additional information is necessary, references to the corresponding documentation is made.

#### 2.2.1 Configuration Steps for Installation

| Configure your controller in accordance with your requirements, also with  |

|----------------------------------------------------------------------------|

| respect to the EHC 105, as described in the "Quantum Hardware Reference    |

| Guide (840 USE 100 00)". Details for connecting signal transmitters to the |

| EHC 105 can be found within the module description in the appendix A       |

| (Module Description).                                                      |

|                                                                            |

|                                                                            |